# Integrated Circuit Cooling Using Heterogeneous Micropin-Fin Arrays for Nonuniform Power Maps

Thomas E. Sarvey, Yuanchen Hu, Craig E. Green, Peter A. Kottke, David C. Woodrum,

Yogendra K. Joshi, *Fellow, IEEE*, Andrei G. Fedorov, Suresh K. Sitaraman,

and Muhammed S. Bakir, *Senior Member, IEEE*

**Abstract**—As microelectronic system density continues to increase, cooling with conventional technologies continues to become more challenging and is often a limiter of performance and efficiency. The challenge arises due to both large heat fluxes generated across entire chips and packages, and localized hotspots with even higher heat flux. In this paper, nonuniform micropin-fin heat sinks are investigated for the cooling of integrated circuits with nonuniform power maps. Four heterogeneous micropin-fin samples were fabricated and tested in single-phase experiments with deionized water to investigate the effectiveness of local micropin-fin clustering for the cooling of hotspots. Cylindrical and hydrofoil micropin-fins were tested, as well as two types of heterogeneous arrays: those with pin-fins clustered directly over the hotspot and those with the high density cluster spanning the entire width of the channel to prevent flow bypass around the cluster. Samples were tested with a uniform nominal heat flux of 250 W/cm<sup>2</sup> as well as a hotspot heat flux of 500 W/cm<sup>2</sup>. Local micropin-fin clustering was found to be an effective method of reducing local thermal resistance with a modest pressure drop penalty.

**Index Terms**—Bosch process, deep reactive ion etching (DRIE), hotspot, microfluidic cooling, micropin-fin.

## I. INTRODUCTION

ONE major barrier to greater performance in modern integrated circuits (ICs) is the challenge of dissipating high heat fluxes and total package powers resulting from both traditional transistor scaling and high system integration density in the form of 2.5-D and 3-D systems. In addition to large average heat fluxes, localized hotspots with heat fluxes many times higher than the average chip heat flux may exist, ultimately setting the thermal envelope for the entire package [1]. Microfluidic cooling is an attractive approach to cooling these modern systems due to its ultralow junction-to-fluid thermal resistance, as well as its very small footprint and compatibility with high-density heterogeneous systems [2], [3].

Manuscript received October 19, 2016; revised March 21, 2017; accepted May 4, 2017. This work was supported by DARPA under ICECool Applications under Grant HR0011-14-1-0002. Recommended for publication by Associate Editor K. Ramakrishna upon evaluation of reviewers' comments. (Corresponding author: Thomas E. Sarvey.)

T. E. Sarvey and M. S. Bakir are with the Department of Electrical and Computer Engineering, Georgia Institute of Technology, Atlanta, GA 30332 USA (e-mail: tsarvey@gatech.edu).

Y. Hu, C. E. Green, P. A. Kottke, D. C. Woodrum, Y. K. Joshi, A. G. Fedorov, and S. K. Sitaraman are with the Department of Mechanical Engineering, Georgia Institute of Technology, Atlanta, GA 30332 USA.

Color versions of one or more of the figures in this paper are available online at <http://ieeexplore.ieee.org>.

Digital Object Identifier 10.1109/TCMT.2017.2704525

Microfluidic cooling was first demonstrated as a method of cooling high-power ICs in [4]. The thermal resistance from the active region to the fluid inlet in such a system can be described as follows:

$$R_{\text{tot}} = R_{\text{cond}} + R_{\text{conv}} + R_{\text{heat}} \quad (1)$$

where  $R_{\text{cond}}$  is the thermal resistance due to conduction through the silicon,  $R_{\text{conv}}$  is the thermal resistance associated with transferring the heat from the silicon to the fluid, and  $R_{\text{heat}}$  is the effective thermal resistance due to heating of the fluid. Since the demonstration in [4], several microfluidic heat sink geometries have been studied, including microchannels, cylindrical micropin-fins, and micropin-fins with several other cross-sectional shapes.

Prasher *et al.* [5] performed single-phase experiments on cylindrical silicon micropin-fin heat sinks with diameters between 50 and 150  $\mu\text{m}$  with water as a coolant. Correlations for friction factor and Nusselt number were developed to address the discrepancy between previously developed correlations and the observed experimental data. Koz and Kosar [6] and Tullius *et al.* [7] also performed parametric simulations of cylindrical micropin-fin arrays to study thermal and hydraulic performance as a function of micropin-fin design.

Brunschwiler *et al.* [8] investigated microchannels and micropin-fins with an emphasis on interlayer cooling in 3-D IC stacks. Inline and staggered micropin-fins were tested with different pitches in addition to micropin-fins with a teardrop shape. Single-phase thermal and hydraulic data were taken with water as a coolant and used to develop correlations for Nusselt number and friction factor as a function of micropin-fin geometry and flow conditions. Kosar and Peles [9] also reported thermal and hydraulic measurements on micropin-fin heat sinks with multiple cross-sectional shapes and reported the ideal shapes as a function of flow conditions. A number of studies have also looked at flow boiling with microchannels and micropin-fins [10], [11].

While previous work has focused primarily on characterizing uniform micropin-fin heat sinks, the diameter, transverse pitch, and longitudinal pitch of the micropin-fins can all be locally varied to create heterogeneous micropin-fin heat sinks. The ability to create heterogeneous microfluidic heat sinks with customizable local heat transfer coefficients is attractive for cooling systems in which power density is not uniform. By tailoring the heat sink design to the power map, temperature uniformity can be improved. Additionally, by only increasing micropin-fin density where needed, total pressure

drop can be minimized. In other words, pin-fin densities that may produce prohibitively high pressure drops when used over the entire chip can be used over a small area.

Several other methods of hotspot mitigation have been explored, including micro thermoelectric coolers (TECs) [12], liquid jet impingement [13]–[15], thin film evaporation [16], dedicated microgap coolers [10], [17], and heat spreading through highly thermally conductive materials, such as graphene [15], [18]. While all of these approaches have their advantages and disadvantages, they all require relatively complicated fabrication processes. Solutions such as TECs (and to some extend heat spreaders) can reduce temperatures of small hotspots, but still require a means of dissipating large background heat fluxes. The microfluidic heat sinks demonstrated in this paper are fabricated with a single etching step and are also compatible with TSVs and 3-D ICs [19].

Green *et al.* [20] used a 3-D strip model in ANSYS FLUENT to investigate the effect of micropin-fin clustering for hotspot cooling. A local doubling of pin-fin density was found to reduce local thermal resistance by a factor of roughly two. The strip model included symmetry constraints on either side, effectively simulating an infinite array of identical “cooling strips,” with a high-density pin-fin cluster spanning that entire channel. More recently, Lorenzini *et al.* [21] performed full-chip flow and heat transfer simulations with cylindrical micropin-fins, showing effective hotspot cooling with locally clustered micropin-fins.

Heterogeneous micropin-fin arrays are used in this paper to cool a uniform background heat flux with a higher heat flux, hotspot region. Since flow could be diverted around a high-density pin-fin cluster not spanning the entire width of the channel, two types of clusters were chosen for experimental investigation: local clustering over the hotspot and clustering spanning the entire width of the channel. Pin-fins with both circular and hydrofoil shaped cross sections were also tested.

This paper is organized as follows. First, an analysis of the effect of lateral heat spreading through the base of the heat sink is presented. Then, fabrication results are shown for micropin-fin arrays fabricated with a wide range of dimensions on a single wafer. Next, a thermal testbed and the four test chips with heterogeneous micropin-fin arrays are described. Finally, thermal measurements of the four different micropin-fin test chips are presented and analyzed.

## II. EFFECT OF HEAT SPREADING

Even with a uniform micropin-fin array, heat spreading through the silicon bulk will act to partially mitigate hotspots. In order to quantify the effect of spreading as a function of base thickness and the ratio of hotspot heat flux to background heat flux, heat transfer simulations were performed with COMSOL 4.3b. A 3-D model of a 1-cm  $\times$  1-cm chip was created with a 500- $\mu\text{m}$   $\times$  500- $\mu\text{m}$  hotspot region in the center. Symmetry boundary conditions were utilized to only simulate a quarter of this geometry. A maximum mesh size of 10  $\mu\text{m}$  was used in the region over the hotspot, and a maximum mesh size of 50  $\mu\text{m}$  was used over the background region, with a maximum growth rate of 1.1 between the two regions.

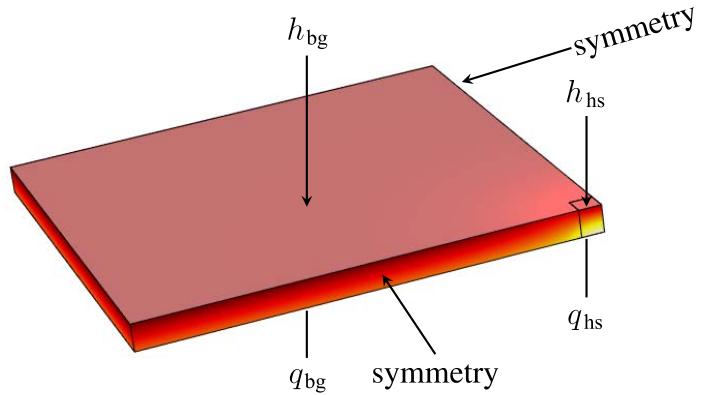

Fig. 1. COMSOL heat spreading model.

On the bottom of the chip slice, two heat fluxes were applied, one to the hotspot ( $q_{hs}$ ) and one to the background region ( $q_{bg}$ ). On the top side of the chip, two heat transfer coefficients were applied, one over the hotspot region ( $h_{hs}$ ), and another over the remaining background region ( $h_{bg}$ ). An illustration of the model can be seen in Fig. 1. The reference temperature on the convective boundary conditions,  $h_{hs}$  and  $h_{bg}$ , was set to a constant 20 °C. Although a microfluidic heat sink would have a gradient in this boundary temperature due to heating of the fluid, using a linear temperature gradient across the chip does not affect the average temperatures in the simulations. The hotspot heat flux can locally heat the fluid, but this effect is expected to be small since the hotspot area is 0.25% of the total chip area. Therefore, the hotspot power is a small fraction of the total power, even when the hotspot heat flux density is several times the average heat flux density.

### A. Effect of Base Thickness on Hotspot Temperature

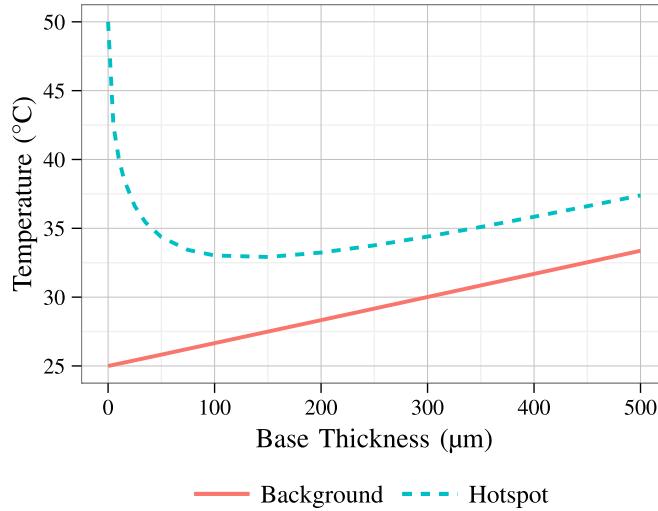

In the first parametric study, the effect of base thickness on hotspot temperature was measured for a silicon thickness range of 0 to 500  $\mu\text{m}$ . The background heat flux was set to 250 W/cm<sup>2</sup>, while the hotspot heat flux was set to 500 W/cm<sup>2</sup>. The background and hotspot heat transfer coefficients were both set to 100 000 W/(°C m<sup>2</sup>), representing a uniform micropin-fin array. Fig. 2 shows the average background and hotspot temperature rise above ambient as a function of base thickness.

The background temperature rise above ambient is approximately a linear function of base thickness due to the conductive thermal resistance of the silicon. The hotspot temperature, on the other hand, initially decreases with increasing silicon base thickness due to lateral heat spreading through the silicon. Spreading then rapidly tapers off with increasing silicon base thickness, and the hotspot temperature reaches a minimum at a thickness of approximately 130  $\mu\text{m}$ . The hotspot temperature then increases with increasing thickness due to the increasing conductive thermal resistance of the silicon.

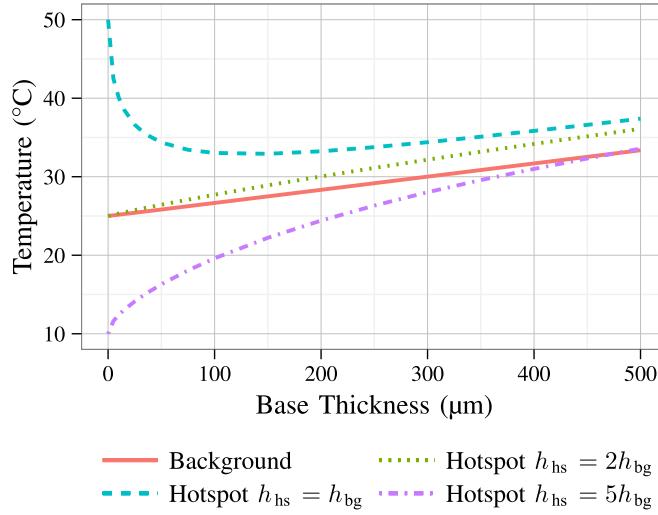

The hotspot temperature can also be influenced by changing the local heat transfer coefficient over the hotspot. Fig. 3 shows the average hotspot and background temperatures when the hotspot heat transfer coefficient is  $1 \times h_{bg}$ ,  $2 \times h_{bg}$ , and  $5 \times h_{bg}$ . The average background temperatures are relatively unaffected

Fig. 2. Simulated surface averaged hotspot and background temperature rise above ambient versus silicon base thickness with uniform heat transfer coefficient [100000 W/(m<sup>2</sup> °C)], hotspot heat flux of 500 W/cm<sup>2</sup>, and background heat flux of 250 W/cm<sup>2</sup>.

Fig. 3. Simulated surface averaged hotspot and background temperature rise above ambient versus silicon base thickness with a hotspot heat flux of 500 W/cm<sup>2</sup>, a background heat flux of 250 W/cm<sup>2</sup>, a background heat transfer coefficient ( $h_{bg}$ ) of 100000 W/(m<sup>2</sup> °C), and hotspot heat transfer coefficients of  $1 \times h_{bg}$ ,  $2 \times h_{bg}$ , and  $5 \times h_{bg}$ .

by the much smaller hotspot conditions, only varying by less than 0.3% between these three cases, so they are drawn as a single line, averaging the three cases. While heat spreading through the base can decrease hotspot temperature with uniform cooling, spreading increases the temperature in the cases with enhanced cooling over the hotspot shown in Fig. 3.

#### B. Measuring Thermal Resistance at the Hotspot

Without heat spreading through the base silicon, one could characterize the heterogeneous heat sink by calculating separate background and hotspot thermal resistances (at specific flow conditions). However, when we define the hotspot thermal resistance as  $R_{hs} = (T_{hs} - T_{amb})/q_{hs}$ , where  $T_{hs}$  is the average

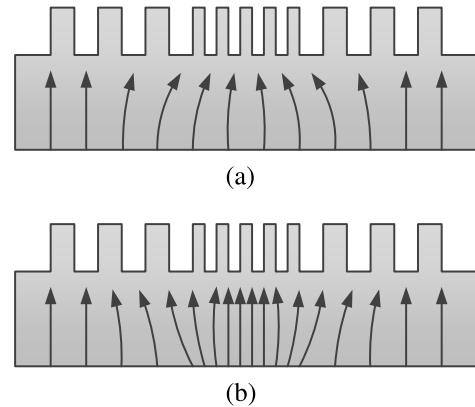

Fig. 4. Direction of heat flow in the substrate for different power maps. (a) Uniform heat flux. (b) High hotspot heat flux.

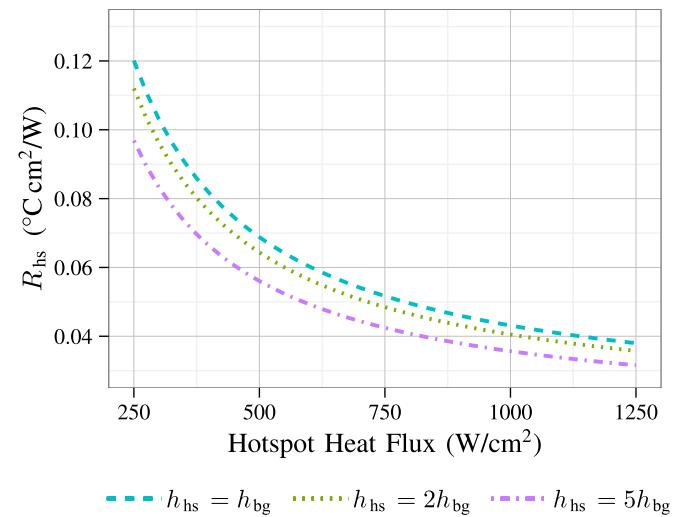

Fig. 5. Effective hotspot thermal resistance ( $R_{hs}$ ) versus hotspot heat flux ( $q_{hs}$ ).

hotspot temperature and  $T_{amb}$  is the reference temperature on the convective boundary condition, the apparent thermal resistance at the hotspot (and to a much lesser extent, the background region) depends on the power map applied. When a uniform power map is applied, some heat from the background region is transferred to the high-density cluster, making the apparent thermal resistance greater than it would be with no spreading (with a very thin base). However, as local heat flux increases, heat begins to leave the dense cluster and finds another path by spreading through the base, causing the apparent thermal resistance to decrease. This effect is illustrated in Fig. 4.

The effective thermal resistance at the hotspot,  $R_{hs}$ , is shown in Fig. 5 where the silicon base thickness is 300 μm and the background heat flux is 250 W/cm<sup>2</sup>. Three lines are shown, where  $h_{hs} = 100000$  W/(m<sup>2</sup> °C),  $h_{hs} = 200000$  W/(m<sup>2</sup> °C), and  $h_{hs} = 500000$  W/(m<sup>2</sup> °C). Due to heat spreading to the surrounding background region, the apparent hotspot thermal resistance changes with hotspot heat flux. Therefore, in Section IV, hotspot performance will be reported as temperatures relative to background temperatures.

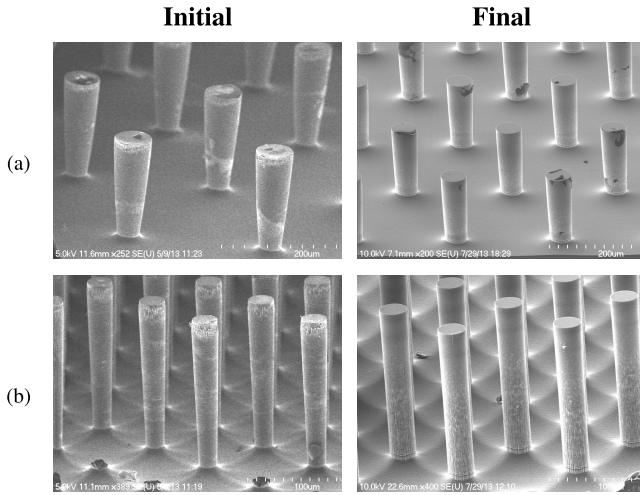

Fig. 6. SEM images of (a) sparse and (b) dense, high-aspect-ratio micropin-fins before and after etching process optimization.

### III. FABRICATION OF MULTIPLE MICROPIN-FIN DENSITIES ON A SINGLE WAFER

In order to locally tailor heat transfer to the fluid, micropin-fins of varying dimensions must be built on the same wafer and, ideally, in the same processing steps. The micropin-fins used in this paper were etched into silicon using the Bosch process and an STS inductively coupled plasma machine. The process consists of a reactive ion etching step with an SF<sub>6</sub> plasma, followed by a passivation step with C<sub>4</sub>F<sub>8</sub>. RF power is applied to the wafer platen in order to create a bias that accelerates ions toward the wafer.

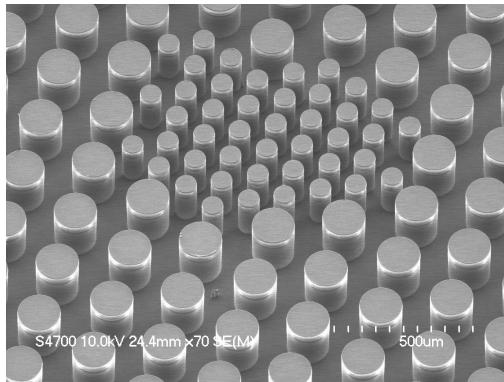

In order to produce heterogeneous micropin-fin arrays, the Bosch process used for etching had to be optimized in order to produce reasonable results for all dimensions with a single wafer-level batch process. This is particularly challenging for high-aspect-ratio micropin-fins, which can be desirable from a thermal perspective for their large surface area. While ideal etching conditions vary between very dense and sparse micropin-fin arrays, a recipe was developed that produced acceptable results for both.

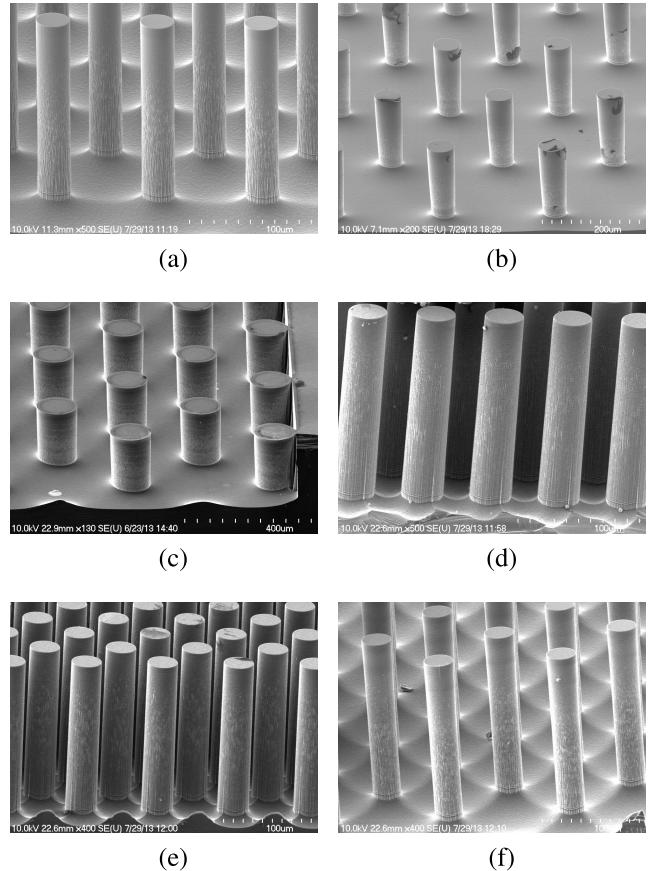

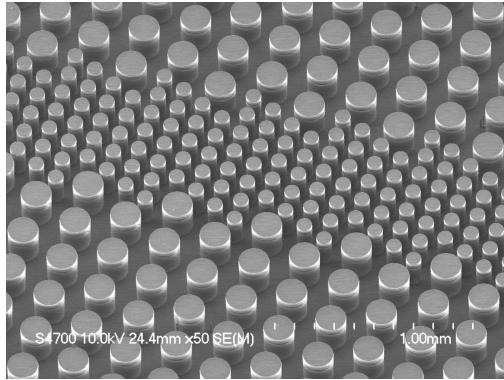

As seen in Fig. 6, the largest issue was micropin-fin sidewall tapering on very sparse micropin-fin arrays. Significant tapering could decrease fin efficiency and produce results that deviate from expected results with cylindrical micropin-fins. This was improved by increasing the ratio of passivation time to etching time. Platen power was increased during the etch step, and the total cycle time was increased relative to the default trench etching recipe, yielding the final etching recipe consisting of a 14-s etch step, a 17.5-s passivation step, and a platen power of 20 W. This recipe was used to produce the results shown in Fig. 7, which shows sidewall profiles of six different micropin-fin arrays built on a single wafer. Dense, sparse, and high-aspect-ratio dimensions are included and can be seen in Table I. Heat transfer and pressure drop studies were carried out with these samples in [22]. Four of the micropin-fin arrays have a micropin-fin diameter of 30 μm, which is substantially smaller than the majority of micropin-fins studied in literature. Since all micropin-fins were etched to a nominal

TABLE I

CYLINDRICAL MICROPIN-FIN DIMENSIONS BUILT ON A SINGLE WAFER

| Die Number | Diameter | Transverse Pitch | Lateral Pitch |

|------------|----------|------------------|---------------|

| Die 1      | 30 μm    | 90 μm            | 90 μm         |

| Die 2      | 60 μm    | 240 μm           | 240 μm        |

| Die 3      | 120 μm   | 420 μm           | 180 μm        |

| Die 4      | 30 μm    | 90 μm            | 30 μm         |

| Die 5      | 30 μm    | 75 μm            | 36 μm         |

| Die 6      | 30 μm    | 120 μm           | 60 μm         |

Fig. 7. Six micropin-fin dice etched using a single-batch process on the same wafer. (a) Die 1. (b) Die 2. (c) Die 3. (d) Die 4. (e) Die 5. (f) Die 6.

height of 200 μm, these small diameter micropin-fins have an aspect ratio of 6.7:1, which is also necessary for high surface area enhancement, but makes sidewall profile crucial.

### IV. THERMAL TESTBED AND HETEROGENEOUS MICROPIN-FIN SAMPLES

In this paper, chip heat flux is represented by a “background” heat flux and a “hotspot” heat flux. The hotspot is a smaller region of the chip, with a heat flux considerably higher than that of the background region. By locally clustering micropin-fins over a hotspot, it is expected that the local heat transfer coefficient can be increased to deal with the hotspot heat fluxes, while minimizing the pressure drop penalty compared to using this high-density clustering over the entire background region.

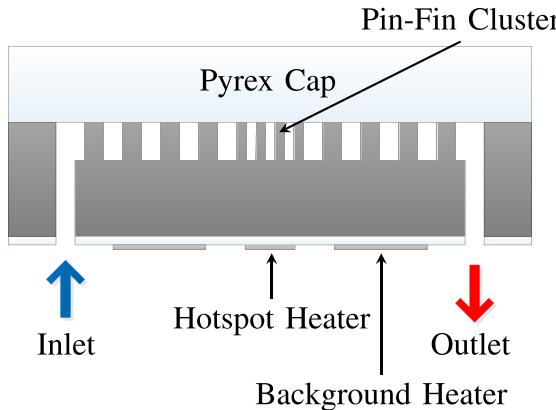

Fig. 8. Heterogeneous micropin-fin test chip cross section.

The etching recipe discussed above was applied to heterogeneous micropin-fin arrays with local clustering of micropin-fins over hotspots. First, the micropin-fins were etched into a 500- $\mu\text{m}$  double-side polished silicon wafer. A pyrex cap was anodically bonded to the micropin-fins to seal the channels. Next, a 1.9- $\mu\text{m}$ -thick silicon dioxide layer was deposited on the back side of the wafer, on top of which 0.2- $\mu\text{m}$ -thick platinum heaters were deposited. The heaters also acted as resistance temperature detectors (RTDs). Finally, fluid inlet/outlet and pressure measurement ports were etched through the silicon. A cross-sectional diagram of the test chips can be seen in Fig. 8.

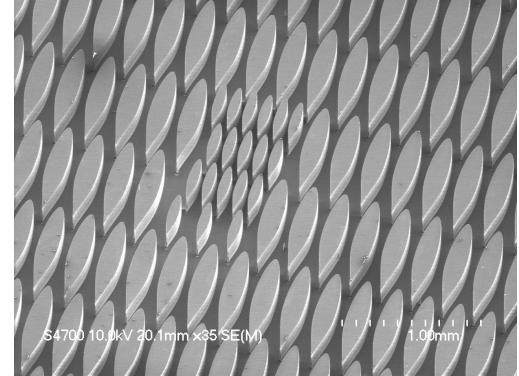

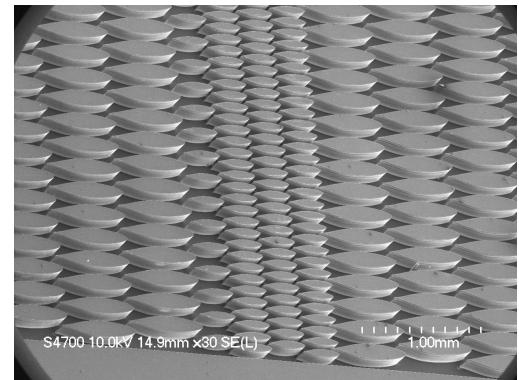

While enhanced heat transfer is only necessary over the hotspot, local clustering over this region is expected to result in some flow diversion around the higher density clustering. Therefore, for both the hydrofoil and circular micropin-fin designs, clustering was done in a small region over the hotspot as well as in a region spanning the entire width of the channel to prevent this flow diversion. Four different background/hotspot test devices were fabricated, with two types of micropin-fin cross-sectional shapes and two types of clustering for hotspot cooling as follows:

- 1) cylindrical micropin-fins with local clustering;

- 2) cylindrical micropin-fins with span-wise clustering;

- 3) hydrofoil micropin-fins with local clustering;

- 4) hydrofoil micropin-fins with span-wise clustering.

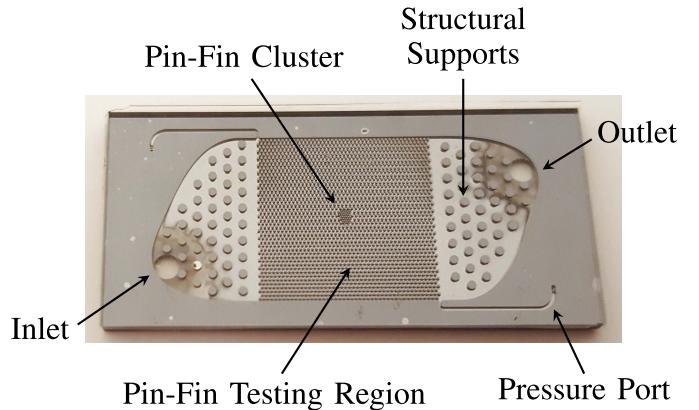

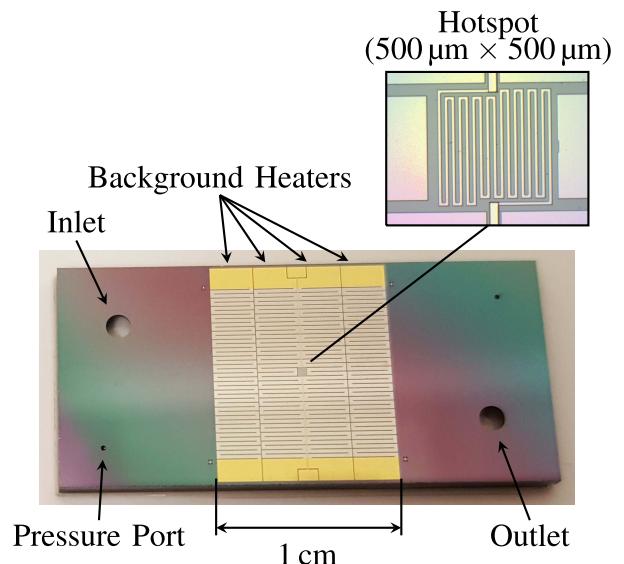

Images of the top and bottom of a micropin-fin test device can be seen in Fig. 9. The background micropin-fin array covers an area of 1 cm  $\times$  1 cm. The hotspot consists of an area of 500  $\mu\text{m}$   $\times$  500  $\mu\text{m}$  in the center of the chip. This region is heated by a dedicated serpentine platinum heater on the bottom of the chip while background heat flux is applied through four heaters spanning the chip. Pressure ports at the inlet and outlet sides of the background micropin-fin array provide accurate pressure drop measurements.

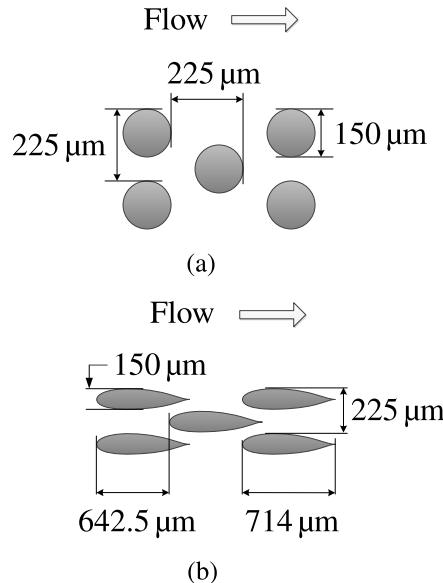

Dimensions of the background micropin-fins can be seen in Fig. 10. The diameter of the cylindrical micropin-fins is 150  $\mu\text{m}$ . The transverse and longitudinal pitches are both 225  $\mu\text{m}$ . The width of the background hydrofoil micropin-fins is 150  $\mu\text{m}$ , and the transverse and longitudinal pitches are 225 and 642.5  $\mu\text{m}$ , respectively. All micropin-fins were

(a) Top side of die with micropin-fins

(b) Bottom side of die with heaters and fluid ports

Fig. 9. Test chip. (a) Top view of etched silicon through pyrex cap. (b) Bottom view of heaters and ports.

etched to a nominal height of 200  $\mu\text{m}$ . Pitches and diameters of micropin-fins in the high-density clusters were half of the background pitches and diameters. SEM images of the micropin-fin clustering over the hotspots for the four different heat sinks can be seen in Figs. 11–14.

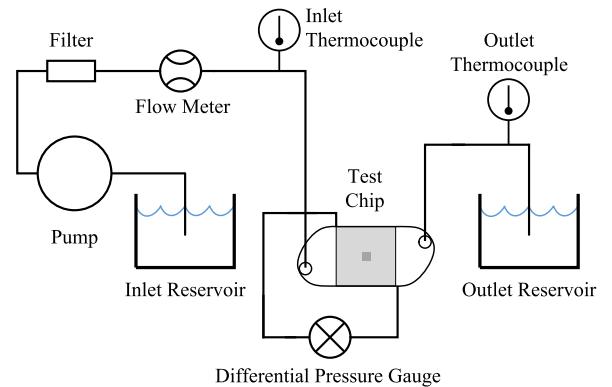

Each chip was tested in an open-loop system with deionized water as a coolant, with an inlet temperature of  $21 \pm 0.5$   $^{\circ}\text{C}$ . A diagram of the open flow loop can be seen in Fig. 15. RTD resistance versus temperature calibration lines were first generated by measuring RTD resistances at temperatures ranging from approximately 20  $^{\circ}\text{C}$  to approximately 110  $^{\circ}\text{C}$ . The chips were placed in a package with O-ring seals on the ports for fluid delivery and pressure measurement. Fluid temperature was measured at the inlet and outlet of the package with k-type thermocouples calibrated to an accuracy of 0.1  $^{\circ}\text{C}$  over the range of temperatures used in experimentation. Flow rate was measured with a rotameter with a maximum uncertainty of less than 2 mL/min. Pressure drop across the micropin-fin arrays was measured using a digital differential pressure gauge

Fig. 10. Background micropin-fin dimensions. (a) Background circular micropin-fin dimensions. (b) Background hydrofoil micropin-fin dimensions.

Fig. 11. Cylindrical micropin-fins locally clustered over hotspot.

Fig. 12. Cylindrical micropin-fins spanning entire channel.

calibrated with an Omega DPI610 calibrator to within 0.1 kPa. RTD power and resistance were recorded with an Agilent data logger.

Each experiment was run twice, and the averages of the results from the two runs are reported in Section V. In order to

Fig. 13. Hydrofoil micropin-fins locally clustered over hotspot.

Fig. 14. Hydrofoil micropin-fins spanning entire channel.

Fig. 15. Diagram of open loop system used to test chips.

quantify the uncertainty in the RTD temperature measurements as well as the pressure measurements, combined standard deviations across these repeated runs were calculated and are reported in Table II along with the measurement device uncertainties.

The amount of heat lost to the ambient surroundings can be calculated from measured quantities according to

$$Q_{\text{loss}} = Q_{\text{in}} - \dot{m}C_p(T_{\text{out}} - T_{\text{in}}) \quad (2)$$

where  $\dot{m}$  is the water mass flow rate,  $C_p$  is the specific heat of water (approximately 4.18 J/(g °C), and  $T_{\text{in}}$  and  $T_{\text{out}}$  are the measured water inlet and outlet temperatures, respectively.

TABLE II

MEASUREMENT UNCERTAINTIES

|                                         |          |

|-----------------------------------------|----------|

| Pressure Gauge Accuracy                 | 0.1 kPa  |

| Thermocouple Measurement Accuracy       | 0.1 °C   |

| Flow Rate Measurement Accuracy          | 2 mL/min |

| Combined Temperature Standard Deviation | 0.33 °C  |

| Combined Pressure Standard Deviation    | 1.3 kPa  |

Heat loss to ambient was found to be below 3.35% for all data points.

Due to the high heat fluxes and low convective thermal resistances in these experiments, temperature drop across the 1.9- $\mu\text{m}$ -thick silicon dioxide insulation under the platinum heaters accounted for a substantial portion of the temperature difference between the RTDs and the fluid. This temperature drop across the silicon dioxide layer was estimated through heat conduction simulations in COMSOL, taking the thermal conductivity of PECVD silicon dioxide to be 1.1 W/(m °C) [23], [24]. Since the serpentine heaters do not provide completely uniform heat flux, the temperature drop across the silicon dioxide is higher than 1-D conduction calculations would predict. The temperature drop from the RTD to the silicon was found to be 7.9 °C and 15.8 °C for nominal hotspot heat fluxes of 250 and 500 W/cm<sup>2</sup>, respectively. From the background RTDs to the silicon, this number was 5.2 °C at 250 W/cm<sup>2</sup>. These numbers were used to compute the temperatures at the silicon surface, called the junction temperature, or  $T_j$ .

## V. EXPERIMENTAL RESULTS

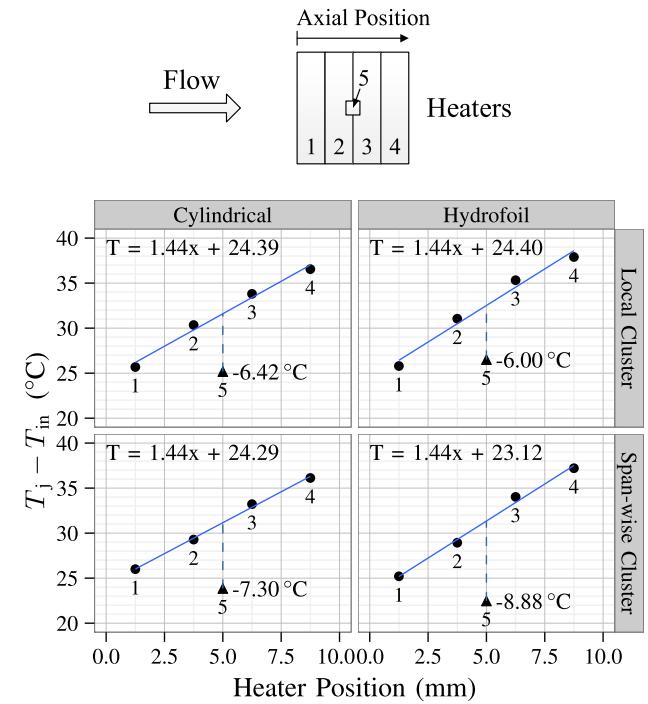

Fig. 16 shows junction temperature rise above inlet temperature ( $T_j - T_{in}$ ) versus axial position in the direction of fluid flow (x) for all four types of chips at a flow rate of 208 mL/min and a uniform power of 246 W across the 1-cm  $\times$  1-cm chips. Maximum variation in heat flux between the four heaters was found to be between 1% and 4%. With a uniform micropin-fin array, uniform power, constant fluid heat capacity, and no edge effects, one would expect the junction temperature to increase linearly with axial position. A line was fit to the four background junction temperatures using least squares. As can be seen, the temperature does rise linearly, although the first and last temperatures tend to be below the fit line, while the center heaters tend to be above. This could be a result of heat spreading to the inlet and outlet plena as well as flow development in these regions.

The slopes of the lines in Fig. 16 have units of °C/mm and depend primarily on flow rate and heat flux rather than the micropin-fin dimensions. As expected, all four lines have the same slope. By multiplying the slope by the length of the chip, the change in fluid temperature across the 1-cm length of the micropin-fin region can be estimated. Since this gradient across the micropin-fin region of the chip only accounts for approximately 85% of the measured  $T_{out} - T_{in}$ , it is estimated that approximately 15% of the heat flux was spread to the inlet and outlet plena where it was transferred to the water.

As can be seen, the background  $T_j$  values for all four chips are very similar. A larger difference can be seen in the hotspot temperatures. Since the hotspots have the same power density

Fig. 16. Junction temperature rise above inlet temperature versus axial position in the direction of fluid flow with a uniform 246-W power. Hotspot labels represent temperature deviation from expected temperature with a uniform micropin-fin density.

Fig. 17. Thermal resistance from the silicon to fluid ( $R_{jf}$ ) versus flow rate for all four dice.

as the rest of the chip for this data set, the temperature would be expected to fall on the best-fit line with uniform micropin-fins. The hotspot temperature deviation from the line is shown on each plot and illustrates the performance improvement from the high-density clustering. All four designs offered a performance improvement through clustering, but the hydrofoil cluster spanning the entire width of the chip performed best, reducing temperature by 8.88 °C versus the background.

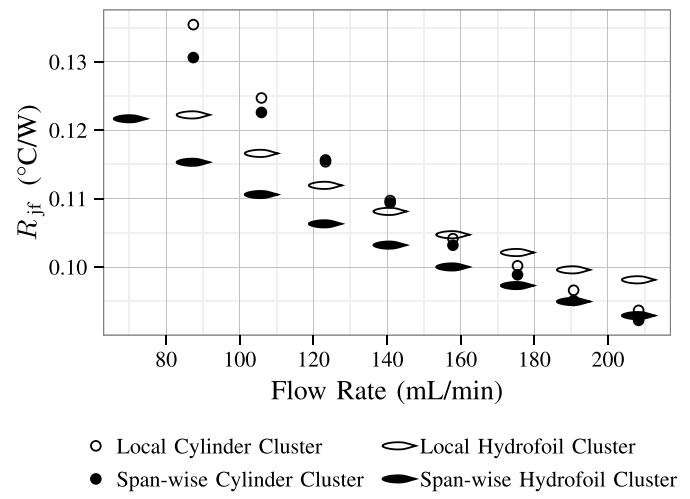

The average background junction-to-fluid thermal resistance,  $R_{jf} = R_{cond} + R_{conv}$ , can be found by subtracting the average fluid temperature from the average junction temperature and dividing by the chip power. Fig. 17 shows background

Fig. 18. Pressure drop versus flow rate for all four dice.

$R_{jf}$  versus flow rate for all four test chips. It should be noted that this includes any effects of the higher density micropin-fin cluster on the background measurements, which can be significant for the micropin-fins spanning the width of the channel, as they cover a larger surface area and are located directly above sections of the background RTDs. Therefore, it is unsurprising that the average background thermal resistance of the hydrofoil sample with span-wise clustering is lower than that of the hydrofoil sample with local clustering, despite the same dimensions of micropin-fins over the rest of the sample.

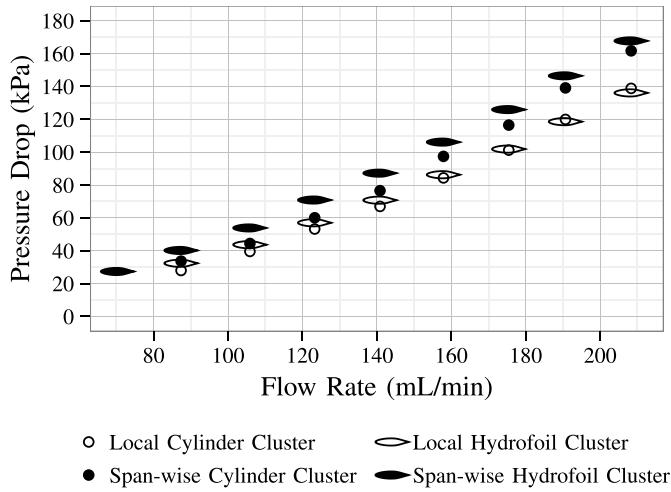

Pressure drop versus flow rate for the four dice can be seen in Fig. 18. The four samples have very similar pressure drops, but, unsurprisingly, the two samples with the high-density clustering spanning the width of the channel have the highest pressure drops. The hydrofoil sample with span-wise clustering had the lowest background and hotspot temperatures, but also had the highest pressure drop.

The Reynolds number was calculated for all four dice. With the characteristic length defined as the hydraulic diameter of the gap between micropin-fins, the Reynolds number ranges from a minimum of 190.5, at the lowest flow rate, to a maximum of 873, at the highest flow rate. Beyond a Reynolds number around 100–300, a flow transition leading to higher pressure drops has previously been observed in micropin-fin arrays [5], [8]. This transition was shown by Renfer *et al.* [25] to occur when the flow transitions from steady laminar flow to a regime with vortex shedding. Since most of the Reynolds numbers in this paper were close to or above this range for all of the flow rates and chips tested, the flow was likely to be in this flow regime with vortex shedding.

#### A. Nonuniform Heat Flux

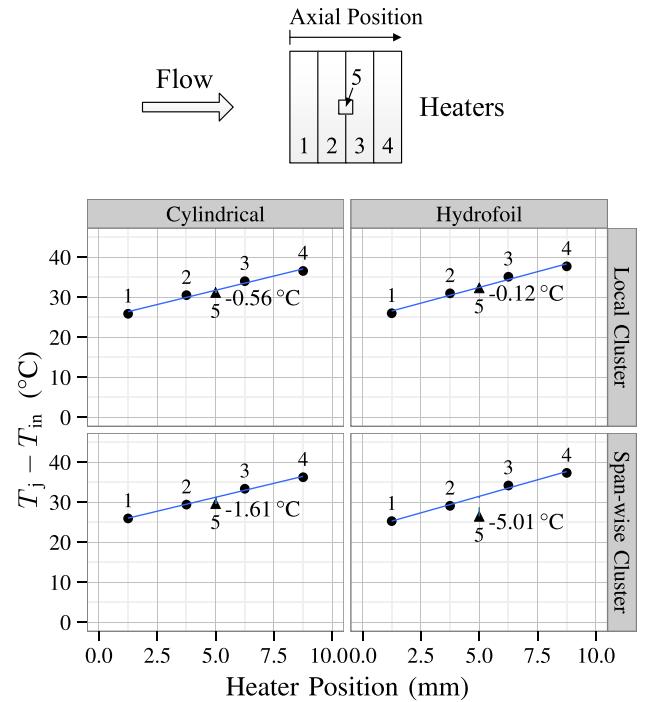

Lastly, all four devices were tested with a nominal background heat flux of  $250 \text{ W/cm}^2$  and a hotspot heat flux of  $500 \text{ W/cm}^2$ . Results at the highest flow rate of  $208 \text{ mL/min}$  can be seen in Fig. 19. Despite doubling the heat flux relative to the background region, hotspot temperatures remain below the background centerline temperatures.

Fig. 19. Junction temperature rise above inlet temperature versus axial position in the direction of fluid flow with  $500 \text{ W/cm}^2$  hotspot heat flux and  $250 \text{ W/cm}^2$  background heat flux. Hotspot labels represent temperature deviation from expected temperature with a uniform micropin-fin density.

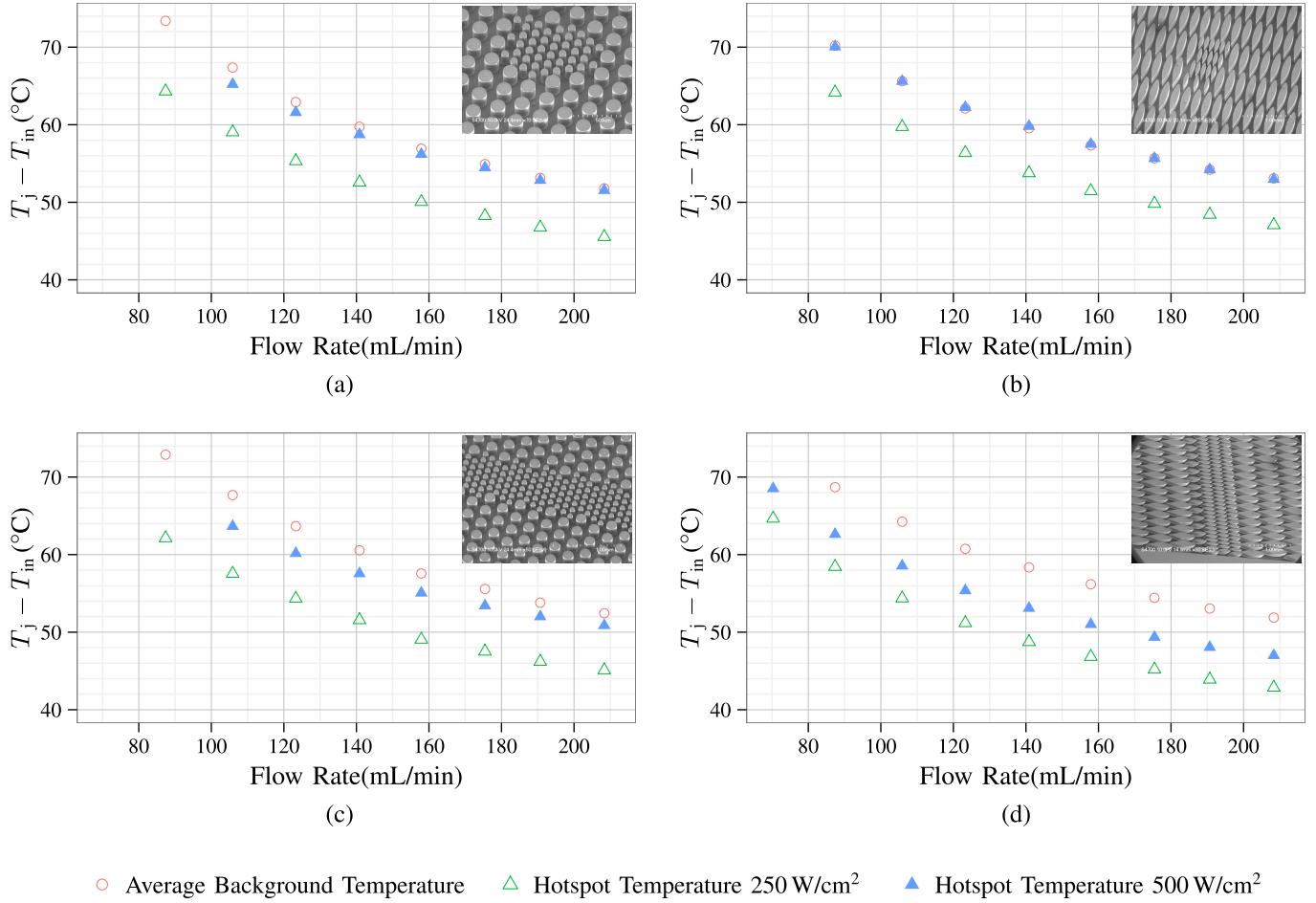

Background and hotspot temperatures are shown for all four devices as a function of flow rate in Fig. 20. Hotspot junction temperature rise above inlet temperature is shown for nominal hotspot heat fluxes of  $250$  and  $500 \text{ W/cm}^2$  with a background heat flux of  $250 \text{ W/cm}^2$ . The average background temperature across all four background heaters is also shown. Since the total hotspot power was much lower than the background power (due to its smaller size), the average background temperature was minimally affected by the hotspot heat flux. Therefore, a single set of background temperature points is shown, representing the average background temperatures between the experiments with the two hotspot heat fluxes. Each of these average background temperature values varies by less than 0.5% from the measured temperatures in either of the experiments.

As can be seen in Fig. 20, the hotspot temperature is lower than the average background temperature for all uniform power maps ( $250 \text{ W/cm}^2$  background and hotspot). When the hotspot heat flux is increased to  $500 \text{ W/cm}^2$ , the hotspot temperature increases, but remains below average background temperature for most of the four device types. The hydrofoil micropin-fins with local clustering have a hotspot temperature that matches the background temperature very closely when the hotspot heat flux is twice the background heat flux (maximum difference of  $0.25 \text{ }^\circ\text{C}$ , or 0.4%). As seen before, the hydrofoil device with high-density micropin-fins spanning the entire width of the channel has the lowest hotspot temperatures and would likely be ideal for even higher hotspot heat fluxes relative to background heat fluxes.

The two devices with micropin-fins spanning the entire width of the channel had lower hotspot temperatures than

Fig. 20. Hotspot and background temperatures versus flow rate of all four chips. (a) Cylindrical micropin-fins with local clustering. (b) Hydrofoil micropin-fins with local clustering. (c) Cylindrical micropin-fins with span-wise clustering. (d) Hydrofoil micropin-fins with span-wise clustering.

those with clustering directly over the hotspot. This could be partially due to flow diversion around the cluster when the cluster does not span the entire width of the channel, but also because of heat spreading to the larger high-density cluster when the cluster extends beyond the hotspot region.

## VI. CONCLUSION

In this paper, heterogeneous micropin-fin arrays were fabricated and tested for the cooling of ICs with hotspots. Two types of micropin-fins (cylindrical and hydrofoil) were tested, each with clustering directly over the hotspot, and clustering spanning the entire width of the channel to prevent flow bypass (a total of four devices).

Of the four devices, the device with the hydrofoil shaped micropin-fins and the dense cluster spanning the entire width of the channel had the lowest hotspot temperatures and the lowest background temperatures at many of the flow rates tested. With a uniform power map and the highest flow rate of 208 mL/min, this sample had a background junction-to-fluid thermal resistance of 0.093 °C cm<sup>2</sup>/W.

All four devices effectively reduced hotspot temperatures. With a nominal hotspot heat flux of 500 W/cm<sup>2</sup> and a nominal background heat flux of 250 W/cm<sup>2</sup>, the average

junction temperatures between the hotspot and background were matched very closely for all flow rates on both the samples with only local clustering directly over the hotspot. Background and hotspot average temperatures, relative to inlet temperature, differed by a maximum of 0.4% for all flow rates with the hydrofoil device.

The two devices with micropin-fins spanning the entire width of the channel had lower hotspot temperatures than those with local clustering, at the cost of higher pressure drop. This difference in hotspot thermal performance may partially result from flow diversion around the local clusters, but also likely arises from heat spreading to areas of the high-density clusters that are not directly above the hotspot.

Heat spreading to larger clustered areas could be utilized in future work with higher density clusters extending beyond the limits of the hotspot in both dimensions. In this paper, average background and hotspot temperatures were used, but more detailed temperature maps could also be investigated to resolve the boundaries between these regions and mitigate maximum temperatures. In fact, continuously varying micropin-fin pitches could also be utilized, potentially eliminating almost all temperature variation across the chip for a given power map.

## REFERENCES

- [1] A. Shakouri and Y. Zhang, "On-chip solid-state cooling for integrated circuits using thin-film microrefrigerators," *IEEE Trans. Compon. Packag. Technol.*, vol. 28, no. 1, pp. 65–69, Mar. 2005.

- [2] T. Brunschwiler *et al.*, "Heat-removal performance scaling of interlayer cooled chip stacks," in *Proc. 12th IEEE Intersoc. Conf. Thermal Thermomech. Phenomena Electron. Syst.*, Las Vegas, NV, USA, Jun. 2010, pp. 1–12.

- [3] T. E. Sarvey *et al.*, "Embedded cooling technologies for densely integrated electronic systems," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Sep. 2015, pp. 1–8.

- [4] D. B. Tuckerman and R. F. W. Pease, "High-performance heat sinking for VLSI," *IEEE Electron Device Lett.*, vol. 2, no. 5, pp. 126–129, May 1981.

- [5] R. Prasher *et al.*, "Nusselt number and friction factor of staggered arrays of low aspect ratio micropin-fins under cross flow for water as fluid," *ASME J. Heat Transf.*, vol. 129, no. 2, pp. 141–153, 2007.

- [6] M. Koz and A. Kosar, "Parameter optimization of a micro heat sink with circular pin-fins," in *Proc. 8th Int. Conf. Nanochannels, Microchannels, Minichannels (ASME)*, Montreal, QC, Canada, Aug. 2010, pp. 531–539.

- [7] J. F. Tullius, T. K. Tullius, and Y. Bayazitoglu, "Optimization of short micro pin fins in minichannels," *Int. J. Heat Mass Transf.*, vol. 55, nos. 15–16, pp. 3921–3932, 2012.

- [8] T. Brunschwiler *et al.*, "Interlayer cooling potential in vertically integrated packages," *Microsyst. Technol.*, vol. 15, no. 1, pp. 57–74, Aug. 2008.

- [9] A. Kosar and Y. Peles, "Micro scale pin fin heat sinks—Parametric performance evaluation study," *IEEE Trans. Compon. Packag. Technol.*, vol. 30, no. 4, pp. 855–865, Dec. 2007.

- [10] C. E. Green *et al.*, "A review of two-phase forced cooling in three-dimensional stacked electronics: Technology integration," *J. Electron. Packag.*, vol. 137, no. 4, p. 040802, 2015.

- [11] X. Han, A. Fedorov, and Y. Joshi, "Flow boiling in microgaps for thermal management of high heat flux microsystems," *J. Electron. Packag.*, vol. 138, no. 4, p. 040801-12, 2016.

- [12] I. Chowdhury *et al.*, "On-chip cooling by superlattice-based thin-film thermoelectrics," *Nature Nanotechnol.*, vol. 4, no. 4, pp. 235–238, Jan. 2009.

- [13] C. Green, A. G. Fedorov, and Y. K. Joshi, "Fluid-to-fluid spot-to-spreader (F2/S2) hybrid heat sink for integrated chip-level and hot spot-level thermal management," *J. Electron. Packag.*, vol. 131, p. 025002, Apr. 2009.

- [14] D. Nikolic, M. Hutchison, P. T. Sapin, and A. J. Robinson, "Hot spot targeting with a liquid impinging jet array waterblock," in *Proc. 15th Int. Workshop Thermal Invest. ICs Syst. (THERMINIC)*, Oct. 2009, pp. 168–173.

- [15] Y. Han, B. L. Lau, and X. Zhang, "Package-level microjet-based hotspot cooling solution for microelectronic devices," *IEEE Electron Device Lett.*, vol. 36, no. 5, pp. 502–504, May 2015.

- [16] S. Narayanan, A. G. Fedorov, and Y. K. Joshi, "On-chip thermal management of hotspots using a perspiration nanopatch," *J. Micromech. Microeng.*, vol. 20, no. 7, p. 075010, 2010.

- [17] M. H. Nasr *et al.*, "Hotspot thermal management with flow boiling of refrigerant in ultrasmall microgaps," *J. Electron. Packag.*, vol. 139, no. 1, p. 011006, 2017.

- [18] Z. Yan, G. Liu, J. M. Khan, and A. A. Balandin, "Graphene quilts for thermal management of high-power GaN transistors," *Nature Commun.*, vol. 3, p. 827, May 2012.

- [19] Y. Zhang, A. Dembla, and M. S. Bakir, "Silicon micropin-fin heat sink with integrated TSVs for 3-D ICs: Tradeoff analysis and experimental testing," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 3, no. 11, pp. 1842–1850, Nov. 2013.

- [20] C. E. Green, P. A. Kottke, T. E. Sarvey, A. G. Fedorov, Y. Joshi, and M. S. Bakir, "Performance and integration implications of addressing localized hotspots through two approaches: Clustering of micro pin-fins and dedicated microgap coolers," in *Proc. ASME Int. Tech. Conf. Exhibit. Packag. Integrat. Electron. Photon. Microsyst. Collocated*, Jul. 2015, p. V001T09A056.

- [21] D. Lorenzini *et al.*, "Embedded single phase microfluidic thermal management for non-uniform heating and hotspots using microgaps with variable pin fin clustering," *Int. J. Heat Mass Transf.*, vol. 103, pp. 1359–1370, Dec. 2016.

- [22] T. E. Sarvey, Y. Zhang, Y. Zhang, H. Oh, and M. S. Bakir, "Thermal and electrical effects of staggered micropin-fin dimensions for cooling of 3D microsystems," in *Proc. IEEE Intersoc. Conf. Thermal Thermomech. Phenomena Electron. Syst. (ITHERM)*, May 2014, pp. 205–212.

- [23] T. Yamane, N. Nagai, S.-I. Katayama, and M. Todoki, "Measurement of thermal conductivity of silicon dioxide thin films using a  $3\omega$  method," *J. Appl. Phys.*, vol. 91, no. 12, pp. 9772–9776, 2002.

- [24] M. B. Kleiner, S. A. Kuhn, and W. Weber, "Thermal conductivity measurements of thin silicon dioxide films in integrated circuits," *IEEE Trans. Electron Devices*, vol. 43, no. 9, pp. 1602–1609, Sep. 1996.

- [25] A. Renfer, M. K. Tiwari, T. Brunschwiler, B. Michel, and D. Poulikakos, "Experimental investigation into vortex structure and pressure drop across microcavities in 3D integrated electronics," *Experim. Fluids*, vol. 51, no. 3, pp. 731–741, 2011.

**Thomas E. Sarvey** received the B.S. degrees in physics and computer engineering from the University of Maryland, College Park, MD, USA, in 2012. He is currently pursuing the Ph.D. degree in electrical and computer engineering with the Georgia Institute of Technology, Atlanta, GA, USA.

His current research interests include densely integrated, 2.5-D, and 3-D, electronic systems and their enabling thermal technologies.

**Yuanchen Hu** received the B.S. and M.S. degrees in mechanical engineering from Wuhan University, Wuhan, China, in 2011 and 2013, respectively. He is currently pursuing the Ph.D. degree in mechanical engineering with the Georgia Institute of Technology, Atlanta, GA, USA.

His current research interests include experiments and simulations centering around microelectronic cooling and hotspot thermal management.

**Craig E. Green** received the B.S. degree from Cornell University, Ithaca, NY, USA, in 2002, and the Ph.D. degree from the Georgia Institute of Technology, Atlanta, GA, USA, in 2012, both in mechanical engineering.

He was with Exelon Corporation, Atlanta, where he was involved in nuclear power. He is currently a Research Engineer with the G.W. Woodruff School of Mechanical Engineering, Georgia Institute of Technology, where he is involved in phase change cooling in microfluidics, nanomaterials, and thermal interfaces. He is the CTO of Carbice Nanotechnologies, Inc., Atlanta, developing nanomaterials solutions for electronic devices. He is the Founder of Invisi Cool LLC, a company that uses thermal storage gels to reduce temperature-induced pain involved with common medical procedures.

**Peter A. Kottke** was born in Virginia Beach, VA, USA. He received the B.S. degree in mechanical engineering from Duke University, Durham, NC, USA, in 1995, and the Ph.D. degree from the Georgia Institute of Technology, Atlanta, GA, USA, in 2004, with a dissertation on the role of tension in the Rheology of liquids. In 2000, he began his graduate studies at the Georgia Tech School of Mechanical Engineering, advised by Dr. Ward Winer and Dr. Scott Bair.

He was with Duke University, on a Navy ROTC scholarship for his undergraduate education. He was with the U.S. Navy as a Nuclear Submarine Officer, concluding with a tour aboard the ballistic missile submarine, U.S.S. Tennessee. He completed his post-doctoral research under the supervision of Dr. A. Fedorov from the George W. Woodruff School of Mechanical Engineering, Georgia Institute of Technology, where he is currently a Senior Research Engineer.

**David C. Woodrum** received the B.S. and M.S. degrees in mechanical engineering from the Georgia Institute of Technology, Atlanta, GA, USA, in 2011 and 2012, respectively, where he is currently pursuing the Ph.D. degree in mechanical engineering under the supervision of Dr. S. Sitaraman.

His current research interests include mechanical reliability of two-phase on-chip microelectronics cooling, specializing in finite-element modeling.

**Yogendra K. Joshi** (SM'03–F'12) received the Ph.D. degree in mechanical engineering and applied mechanics from the University of Pennsylvania, Philadelphia, PA, USA, in 1984.

He is currently a Professor and John M. McKenney and Warren D. Shiver Distinguished Chair with the G. W. Woodruff School of Mechanical Engineering, Georgia Institute of Technology, Atlanta, GA, USA. He is the Principal Investigator with the Office of Naval Research Consortium for Resource-Secure Outposts, and the Site Director with the National

Science Foundation Industry/University Cooperative Research Center on Energy Efficient Electronic Systems, Georgia Institute of Technology. His current research interests include the multiscale thermal management.

Dr. Joshi is an elected Fellow of the American Society of Mechanical Engineering (ASME) and the American Association for the Advancement of Science. He was a co-recipient of the ASME Curriculum Innovation Award (1999), the Inventor Recognition Award from the Semiconductor Research Corporation (2001), the ASME Electronic and Photonic Packaging Division Outstanding Contribution Award in Thermal Management (2006), the ASME *Journal of Electronics Packaging* Best Paper of the Year Award (2008), the IBM Faculty Award (2008), the IEEE Semi-Therm Significant Contributor Award (2009), the IIT Kanpur Distinguished Alumnus Award (2011), the ASME InterPack Achievement Award (2011), the ITherm Achievement Award (2012), and the ASME Heat Transfer Memorial Award (2013).

**Andrei G. Fedorov** is currently the Woodruff Professor with the School of Mechanical Engineering and the Petit Institute for Bioengineering and Biosciences, Georgia Institute of Technology, Atlanta, GA, USA, where he has been on faculty since 2000. He has started two technology companies, in the space of gene/drug delivery microarrays and thermal management for laser medicine, to commercialize his inventions. He has authored or co-authored over 200 archival articles in premier technical journals and refereed conference proceedings,

along with numerous invited and keynote presentations at major national and international conferences. He holds 27 U.S. patents. His current research interests include MEMS-enabled bioanalytical instrumentation, electron-beam-mediated nanomanufacturing, thermal management of high power generation devices, and portable/distributed power generation with synergetic CO<sub>2</sub> capture.

Dr. Fedorov is a member of the International Advisory Board of the Tokyo Tech's Global Center of Excellence for Energy Science. He was a recipient of the 2006 Branimir F. von Turkovich Outstanding Young Manufacturing Engineer Award from the Society of Manufacturing Engineers "for contributions and accomplishments in the manufacturing industry," the 2007 Bergles-Rohsenow Award in Heat Transfer from the American Society of Mechanical Engineers for "sustained contribution to heat, mass, and radiation transfer," the 2010 Gustus L. Larson Memorial Award, given jointly by Pi Tau Sigma (International Mechanical Engineering Honor Society) and the ASME, in recognition of outstanding achievements in mechanical engineering within 10 to 20 years following graduation. He serves on the Board of Directors of Horizon Theater Company, a leading contemporary theater in the Southeast of the U.S. He serves on the Editorial Advisory Boards of the *International Journal of Multiscale Computational Engineering*, the *International Journal of Interfacial Phenomena and Heat Transfer*, the *Journal of Nanoelectronics and Optoelectronics*, and the *Transactions of the Japanese Society of Mechanical Engineers*. He consults for a number of government agencies and major

corporations worldwide. For his inventions of biomedical devices, the World Technology Network (WTN), in cooperation with Science Magazine, CNN, and leading technology companies, selected him as a WTN Associate and one of the 25 "most innovative people and organizations in the science and technology world" nominated for the 2005 World Technology Award in Health and Medicine. He was an Invited Participant at the 2006 National Academy of Engineering Frontiers of Engineering Symposium. He was recognized with the U.S. National Aeronautics and Space Administration Invention and Contribution Board Award for the development of catalytic reactor technologies, as well as multiple inventor recognition awards from the Semiconductor Research Corporation and Microelectronics Advanced Research Corporation.

**Suresh K. Sitaraman** received the B.Eng. degree from the University of Madras, Chennai, India, the M.A. and M.S. degrees from the University of Ottawa, Ottawa, ON, Canada, and the Ph.D. degree from The Ohio State University, Columbus, OH, USA, all in mechanical engineering.

He was with IBM in Endicott, NY, USA, and Austin, TX, USA. He joined the George W. Woodruff School of Mechanical Engineering, Georgia Institute of Technology, Atlanta, GA, USA, in 1995, where he is currently the Morris M. Bryan, Jr. Professor. His current research interests include the fabrication, characterization, thermomechanical modeling, and reliable design of microscale and nanoscale structures intended for a wide range of applications.

Dr. Sitaraman is an ASME Fellow. He was a recipient of the Outstanding Achievement in Research Program Development Award from the Georgia Institute of Technology in 2017, the ASME/Electronic and Photonic Packaging Division Applied Mechanics Award in 2012, the Thomas French Achievement Award from the Department of Mechanical and Aerospace Engineering, The Ohio State University, in 2012, the Sustained Research Award from the Georgia Institute of Technology–Sigma Xi in 2008, the Outstanding Faculty Leadership Award for the Development of Graduate Research Assistants from the Georgia Institute of Technology in 2006, the Metro-Atlanta Engineer of the Year in Education Award in 1999, and the NSF-CAREER Award in 1997. His coauthored papers have won the Commendable Paper Award from the IEEE TRANSACTIONS ON ADVANCED PACKAGING in 2004 and the Best Paper Award from the IEEE TRANSACTIONS ON COMPONENTS AND PACKAGING TECHNOLOGIES in 2001 and 2000. He serves as an Associate Editor of the IEEE TRANSACTIONS ON COMPONENTS, PACKAGING, AND MANUFACTURING TECHNOLOGY.

**Muhammed S. Bakir** (SM'12) received the B.E.E. degree from Auburn University, Auburn, AL, USA, in 1999, and the M.S. and Ph.D. degrees in electrical and computer engineering from the Georgia Institute of Technology, Atlanta, GA, USA, in 2000 and 2003, respectively.

He is currently a Professor with the School of Electrical and Computer Engineering, Georgia Institute of Technology. His current research interests include 3-D electronic system integration, advanced cooling and power delivery for 3-D systems, biosensors and their integration with CMOS circuitry, and nanofabrication technology.

Dr. Bakir was a recipient of the 2013 Intel Early Career Faculty Honor Award, the 2012 DARPA Young Faculty Award, and the 2011 IEEE CPMT Society Outstanding Young Engineer Award. He was an Invited Participant in the 2012 National Academy of Engineering Frontiers of Engineering Symposium. In 2015, he was elected by the IEEE CPMT Society as a Distinguished Lecturer and an Invited Speaker at the U.S. National Academies Frontiers of Sensor Science Symposium. He and his research group have received more than 20 conference and student paper awards, including six from the IEEE Electronic Components and Technology Conference, four from the IEEE International Interconnect Technology Conference, and one from the IEEE Custom Integrated Circuits Conference. His group was awarded the 2014 Best Paper of the IEEE TRANSACTIONS ON COMPONENTS, PACKAGING, AND MANUFACTURING TECHNOLOGY in the area of advanced packaging. He is an Editor of the IEEE TRANSACTIONS ON ELECTRON DEVICES and an Associate Editor of the IEEE TRANSACTIONS ON COMPONENTS, PACKAGING, AND MANUFACTURING TECHNOLOGY.